デジタルマルチメータの基礎と概要 Part2 (第2回)

<連載記事一覧>

第1回:「はじめに」「さまざまな電圧測定器」「デジタルマルチメータの形態」「デジタルマルチメータ選定の視点」「【コラム】電子測定器の進化をリードしているキーサイト・テクノロジー」

第2回:「デジタルマルチメータの内部構造」「デジタルマルチメータでの主な測定」「測定結果の記録/保存」「【コラム】各社のデジタルマルチメータとその他の電圧電流測定器」

デジタルマルチメータの内部構造

デジタルマルチメータは比較的シンプルなデジタル化された測定器である。ここではデジタルマルチメータの内部構造について紹介する。

システム構成

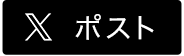

ここではブロック図が公開されているキーサイト・テクノロジーの34401Aの構造を示す。

図23. デジタルマルチメータのブロック図34401A(キーサイト・テクノロジー)

注:34401Aのフロック図や回路図は「Keysight 34401A 6½ Digit Multimeter Service Guide」に公開されている。

基本は直流電圧を測定する入力回路、A/D変換器、制御回路、絶縁回路、表示器、通信ポート、操作パネル、電源となっている。基本回路に電流を測定するためのシャント抵抗、交流を直流に変換する回路、抵抗を測定するための直流電圧発生回路が搭載されてデジタルマルチメータが構成されている。入力端子は絶縁されているため内部の途中に絶縁回路が存在するが、どの部分で絶縁するかは製品によって異なる。

A/D変換器

デジタル化された測定器にはさまざまな種類のA/D変換器が使われている。測定対象によって要求される周波数帯域や分解能が異なるため、利用されるA/D変換器は目的にあった種類が選ばれる。下記には現在測定器でよく使われるA/D変換器を示す。

特にΔΣ(デルタ・シグマ)型A/D変換器とフラッシュ型A/D変換器は半導体技術の進歩によって高性能になり、測定器の進化に貢献している。

|

分解能 (bit) |

変換速度 | 特長 | |

|---|---|---|---|

| 積分型 | 12~20 | 低速 | 耐ノイズ特性がよく、直流の測定では最も高精度 |

| ΔΣ型 | 12~32 | 低速~中速 | アナログ回路規模は極めて小さく LSI 化に最適 |

| 逐次比較型 | 8~18 | 中速 | 回路構成が単純で中速に向く、FFTアナライザで利用 |

| フラッシュ型 | 6~10 | 高速 | 消費電力は大きいが高速に向く、オシロスコープで利用 |

デジタルマルチメータにとってもっと重要な回路は高分解能A/D変換器であり、古い製品ではデュアルスロープ(二重積分)型A/D変換器が多く使われていたが、現在ではデュアルスロープ型を進化させたマルチスロープ型A/D変換器と安価で高分解能が可能なΔ∑(デルタ・シグマ)型A/D変換器がデジタルマルチメータに使われている。

Δ∑(デルタ・シグマ)型A/D変換器の表現

日本国内ではデルタ・シグマ型と言われるが、海外ではシグマ・デルタ型と言われることが多い。日本だけが固有な言い方をするのは「デルタ・シグマ変調方式」を発明した早稲田大学名誉教授の安田靖彦氏が最初に使った表現を尊重してデルタ・シグマと表現している。

マルチスロープ型A/D変換器は耐ノイズが高く、高分解能で測定できるため、8.5桁クラスなどの高性能デジタルマルチメータに採用されている。デュアルスロープ型やマルチスロープ型はアナログ回路の性能に依存する要素が多いため、部品の選定と回路の制御が重要となる。

Δ∑型A/D変換器回路はアナログ部品の選定がデュアルスロープ型やマルチスロープ型に比べて厳しくないこと、回路の集積化が可能なためハンドヘルド型デジタルマルチメータから、6.5桁程度のデスクトップ型デジタルマルチメータまで多く採用されている。

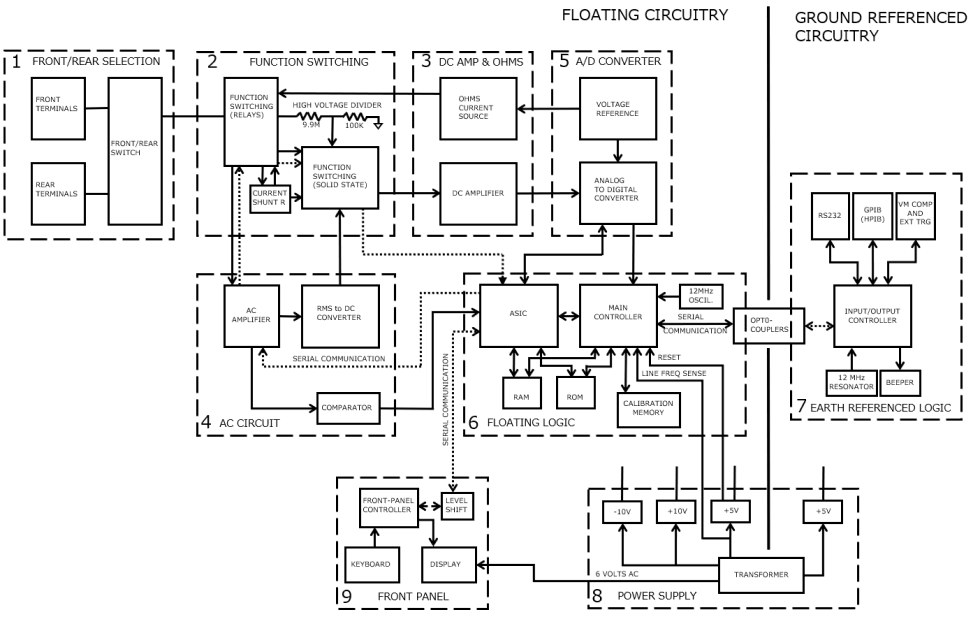

まず、デュアルスロープ型A/D変換器を進化させたマルチスロープA/D変換器について説明する。1957年にギルバート(Rosewell Gilbert)によって発明されたデュアルスロープ型A/D変換器の基本構造を示す。

図24. デュアルスロープA/D変換器の基本回路

未知の電圧VinでコンデンサCに電荷を一定時間tu掛けて充電し、その後既知の電圧Vrefに切り替えて電荷を定電流で0Vまで放電する。放電時間tdをカウンタによって時間測定すれば未知の電圧Vinの電圧値を知ることができる仕組みとなっている。Vinに交流電源からのノイズが重畳しても充電する時間を交流電源の周期の整数倍とすることによって影響を排除することができる特長を持つ。

A/D変換器の分解能をあげるには充電する電荷を増やす必要があるが、充電する電圧が高くなり理想的な積分動作を得ることが難しくなることと、放電に時間が掛かるため測定時間は長くなる課題が生じる。

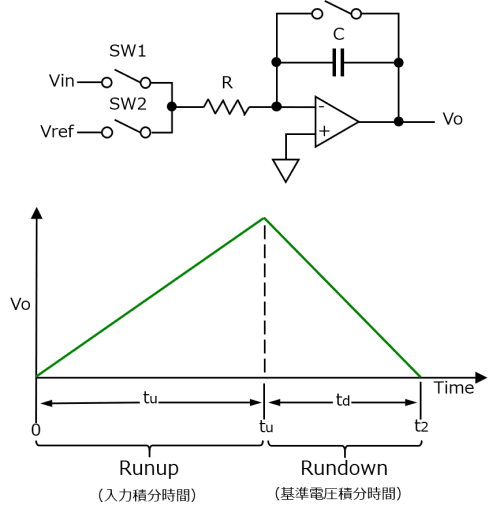

分解能と測定速度を上げるために考えられたのが、マルチスロープ型A/D変換器である。マルチスロープ型A/D変換器の動作については「HEWLETT-PACKARD JOURNAL APRIL 1989」に掲載されている記事「An 8½-Digital Integrating Analog-to-Digital Converter with 16-Bit, 100,000-Sample-per-Second Performance」や米国特許「INTEGRATING ANALOG TO DIGITAL CONVERTER(米国特許番号:5,101,206、Hewlett-Packard Company)」に詳しく書かれている。ここでは概要のみを示すので、詳しく知りたい方は上記資料を参照されることを勧める。

デュアルスロープ型A/D変換器の入力積分動作(Runup)と基準電圧積分時間(Rundown)の動作を改善することによって、高分解能と高速動作をともに実現できるようにした。

入力積分動作(Runup)の動作を改善するために、積分回路に正および負の基準電圧がRaとRbを介して印加されるようにする。RaとRbはRiより小さい抵抗とする。

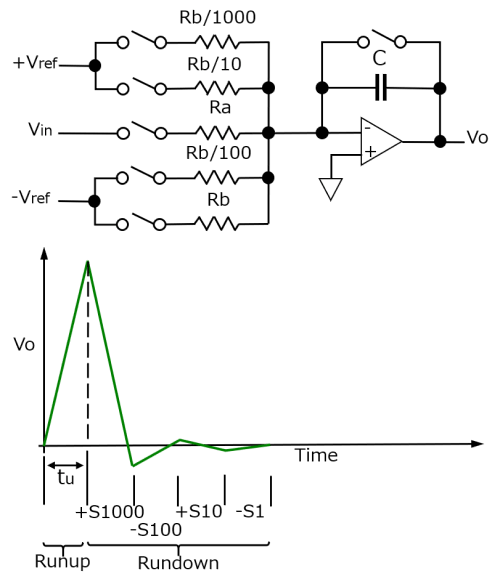

図25. マルチスロープA/D変換器の入力積分動作(Runup)回路と動作

積分器の出力Voの値を破線で示す時点で0Vを横切った場合は極性を反転させるために基準電圧の極性を変える。このような動作を行うことによって積分電圧範囲を見かけ上大きくすることができる。

入力積分動作(Runup)の動作で得られた情報に残留電圧を加えたものが測定結果となる。基準電圧積分時間(Rundown)を短縮するために、下図に示すように複数の電流値によって高速に放電を行う制御をする。

図26. マルチスロープA/D変換器の基準電圧積分時間(Rundown)回路と動作

図に示すように最初は大きな放電レートで電荷減少させ、0Vを横切った後に放電レートを少なくして定電流で充電して0Vを横切るまで充電を続ける。この動作を繰り返してそれぞれの充電と放電の時間から残留電圧の値を求める。

マルチスロープA/D変換器は特性のよいアナログ部品が必要で、誤差を生じさせないための制御が難しいため、高性能なデジタルマルチメータに使われることが一般的である。

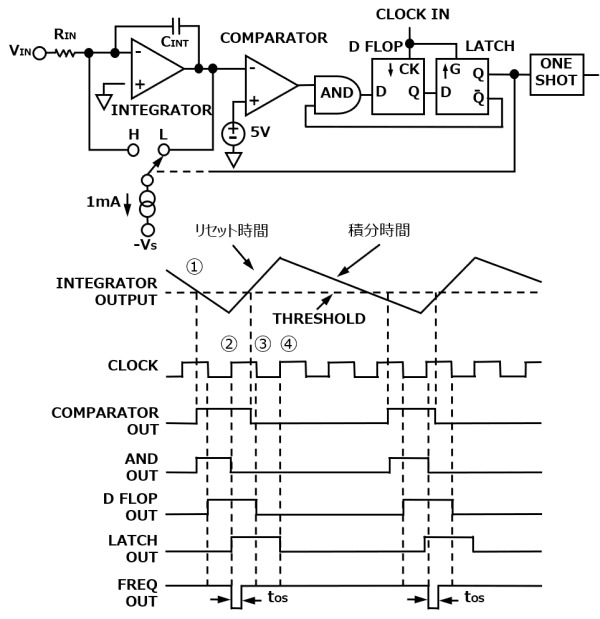

最近のハンドヘルド型からベンチトップ型までの多くのデジタルマルチメータはΔΣ型A/D変換器を搭載している。ここではアナログ・デバイセズのAD652を例にΔΣ型A/D変換器を使っての直流電圧測定の動作を説明する。

図27. ΔΣ型A/D変換器での直流電圧測定

出典:ΔΣ型が積分型にとって代わる理由(松井 邦彦 トランジスタ技術 2008年5月号)

積分器の出力が5Vまで下ると、コンパレータ出力はL→Hになる。

AND出力がHになると、次のクロックの立ち下りでDフリップフロップの出力がHとなる。

次のクロックの立ち上りでラッチ出力QがHとなり、スイッチSWがONにして積分器をリセットする。

同時にANDゲート出力をLにする。

次のクロックの立ち下りでDフリップフロップの出力がLになる。

次のクロックの立ち上りでラッチ出力はLとなり、アナログスイッチをOFFにして積分モードにする。

リセット時間Tresの間に上昇した積分器の出力電圧ΔVを入力電流Iinによって打ち消す動作を繰り返す。

Iref:基準電流

ΔVを入力電流Iinによって打ち消す時間t1は次のようになる。

従って、出力周波数foutがVinに比例することになる。

上記の関係が成り立つため、下記が成立する

foutをカウンタで周波数を測定することによって入力電圧を知ることができる。

デジタル制御回路

デジタルマルチメータは測定した結果をスケーリングして数字表示させるため、デジタル回路が必要となる。初期のデジタルマルチメータはマイクロプロセッサを搭載していなかったが、デジタルマルチメータにGP-IBによる通信機能が搭載されるようになると、マイクロプロセッサが搭載されるようになった。

マイクロプロセッサの高性能化によりデジタルマルチメータにさまざまな機能が搭載されるようになり、測定結果の統計処理や生産ラインで要求される判定出力機能を搭載した製品もある。

pc.png)